что такое мдп логика

Комплиментарная МДП логика

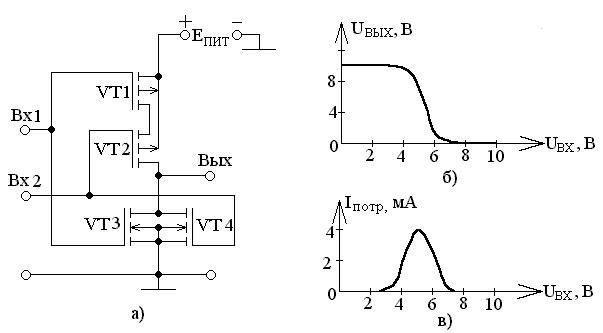

Комплиментарная МДП (КМДП) логика включает в себя пары p- и n-канальных полевых транзисторов с индуцированным каналом. Простейшая схема, выполняющая операцию НЕ представлена на рисунке 1.18а.

Принцип её работы поясним с помощью таблицы 1.10.

| Вх | UВХ, В | VT1 | VT2 | IС | UВЫХ, В | Вых |

| Откр | Закр | |||||

| Закр | Откр |

Предположим, что напряжение питания равно ЕПИТ=10 В. Как будет показано ниже напряжение U 0 =0 В, а U 1 =10 В. Пороговое напряжение, подаваемое на затвор, у таких транзисторов составляет примерно UЗИ ПОРОГ » 4 В. Тогда при подаче на вход напряжения логического ²0² (первая строчка таблицы) транзистор VT2 будет закрыт, а транзистор VT1 будет открыт. Так как напряжение между его затвором и истоком, который соединен с подложкой, равно UЗИ=-10 В, а пороговое напряжение для р-канального транзистора составляет UЗИ ПОРОГ »-4 В. Поскольку транзистор VT2 закрыт, ток стока IС=0. Напряжение на выходе составит UВЫХ= 10 В и, следовательно, это соответствует логической ²1².

При подаче на вход логической ²1² U 1 =10 В (вторая строчка таблицы) транзистор VT1 будет закрыт, поскольку напряжение между его затвором и истоком составляет UЗИ=0 В, а транзистор VT2 будет открыт. Так как транзистор VT1 закрыт, ток стока так же будет равен IС=0. Напряжение на выходе составит UВЫХ= 0 В и, следовательно, это соответствует логическому ²0². Таким образом, в статическом состоянии ток через схему отсутствует за исключением тока утечки, который составляет единицы мкА.

Рассмотрим схему, приведенную на рисунке 1.18б. Принцип её работы также поясним с помощью таблицы 1.11.

| Вх 1 | Вх 2 | UВХ 1, В | UВХ 2, В | VT1 | VT2 | VT3 | VT4 | I | UВЫХ, В | Вых |

| Откр | Откр | Закр | Закр | |||||||

| Закр | Откр | Откр | Закр | |||||||

| Откр | Закр | Закр | Откр | |||||||

| Закр | Закр | Откр | Откр |

При подаче на оба входа логического ²0², как было рассмотрено выше транзисторы VT1 и VT2 открыты, а транзисторы VT3 и VT4 закрыты. На выходе будет высокий потенциал и ток через схему отсутствует (первая строчка таблицы 1.11).

При подаче на вход хотя бы одной логической ²1² один из транзисторов VT3 или VT4 открывается, а один из транзисторов VT1 или VT2 закрывается. Поскольку один из транзисторов закрыт VT3 или VT4, то ток через схему отсутствует, а на выходе будет высокий потенциал, т.е. логическая ²1² (вторая и третья строка таблицы).

При подаче на оба входа логических ²1² оба транзистора VT3 и VT4 открыты, а транзисторы VT1 и VT2 закрыты. На выходе будет логический ²0² и ток через транзисторы по-прежнему отсутствует (четвертая строчка таблицы). Таким образом, данная схема выполняет операцию И-НЕ. В статическом режиме она не потребляет тока.

Схема ИЛИ-НЕ представлена на рисунке 1.19а, а её принцип работы поясним с помощью таблицы 1.12.

| Вх 1 | Вх 2 | UВХ 1, В | UВХ 2, В | VT1 | VT2 | VT3 | VT4 | I | UВЫХ, В | Вых |

| Откр | Откр | Закр | Закр | |||||||

| Закр | Откр | Откр | Закр | |||||||

| Откр | Закр | Закр | Откр | |||||||

| Закр | Закр | Откр | Откр |

В этом случае, в отличие от предыдущего, при подаче на один из входов логической ²1²(вторая и третья строчки таблицы) на выходе будет логический ²0², так как один из транзисторов VT1 и VT2 закрыт, а один из транзисторов VT3 или VT4 открыт, т.е. на выходе будет нулевой потенциал.

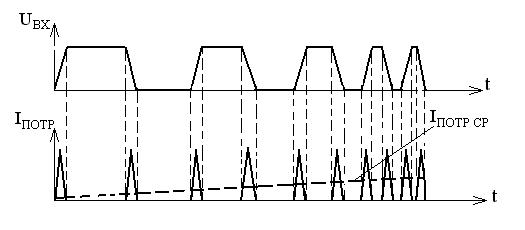

Характеристика прямой передачи приведена на рисунке 1.19б. При подаче низкого потенциала на вход, как было показано выше, на выходе будет высокий потенциал (логическая ²1²). Увеличивая напряжения на входе (при достижении порогового напряжения) открываются транзисторы VT3 и VT4 и начинают закрываться транзисторы VT1 и VT2, напряжение на выходе падает до нуля. Аналогично можно и объяснить характеристику тока потребления от входного напряжения (рисунок 1.19в), т.е. при напряжении от 3 до 7 вольт все транзисторы ²приоткрыты² и в этом случае через схему протекает ток. Это приводит к тому, что при увеличении частоты переключения средний ток, потребляемый схемой, увеличивается (рисунок 1.20) и на высоких частотах он может сравняться с током потребления ТТЛ и ТТЛШ.

Ниже приведены параметры некоторых серий микросхем КМДП. Средний ток потребления от источника питания IПОТР СР приведен в статическом режиме. Из таблицы видно, что с совершенствованием технологии растут энергетические показатели.

Цифровые интегральные логические элементы

В процессе развития интегральной электроники выделилось несколько типов схем логических элементов, имеющих достаточно хорошие характеристики и удобных для реализации в интегральном исполнении, которые служат элементной базой современных цифровых микросхем.

Базовые элементы, независимо от их микросхемотехники и особенностей технологий изготовления, строятся в одном из базисов (как правило, в базисе И – НЕ или ИЛИ – НЕ ).

Базовые элементы выпускаются в виде отдельных микросхем, либо входят в состав функциональных узлов и блоков, реализованных в виде СИС, БИС, СБИС.

Входная логика может быть выполнена на диодах, биполярных и полевых транзисторах. В зависимости от этого различают:

В перечисленных группах логических элементов в качестве выходного каскада используется ключевая схема (инвертор). Другая группа логических элементов основана на переключателях тока – эмиттерно-связанная логика (ЭСЛ-логика).

Транзисторно-транзисторная логика (ТТЛ)

Рис. 17. Базовый элемент ТТЛ

При подаче низкого потенциала логического нуля хотя бы на один из входов открывается этот переход эмиттер–база транзистора Т1, появляется значительный ток I э и потенциал в точке A, равный

Существенным недостатком рассмотренной схемы элемента И–НЕ являются низкие нагрузочная способность и экономичность ее инвертора, поэтому в практических схемах используют более сложный инвертор.

В конце 70-х годов началось широкое применение серий элементов на транзисторах Шоттки с повышенным быстродействием за счет уменьшения задержки выключения ключей. По принципу действия базовый элемент ТТЛШ аналогичен ТТЛ-элементу.

Необходимо заметить, что схемам ТТЛ и ТТЛШ свойственен большой логический перепад напряжений, равный

Интегральная инжекционная логика (И 2 Л)

Схемы И 2 Л не имеют аналогов в дискретных транзисторных схемах, т. е. характерны именно для интегрального исполнения. Основой И 2 Л элементов является инвертор (рис. 18), составленный из двух транзисторов.

Рис. 18. Базовый элемент инжекционной логики

Транзистор Т1 является транзистором n-p-n типа, а транзистор Т2 – p-n-p типа, причем одна из областей n-типа является как базой транзистора Т1, называемого инжектором (отсюда и название логики), так и эмиттером транзистора Т2, а база транзистора Т2 является коллектором инжектора. Функционально транзистор Т1 выполняет роль нагрузочного резистора, а Т2 – полупроводникового ключа.

Выходной транзистор – многоколлекторный, что обеспечивает развязку выходов друг от друга. Если ключевой транзистор предыдущей схемы открыт, то через него замыкается на корпус ток I к транзистора Т1, заданный внешним источником тока, и не поступает в базу транзистора Т2, оставляя его закрытым.

Рис. 19. Реализация схемы ИЛИ–НЕ в логике И 2 Л

В качестве источников тока питания I ип служат генераторы токов на p-n-p транзисторах, включенных по схеме с общей базой. Из-за отсутствия в схеме резисторов и общих для обоих транзисторов областей p и n-типа схема очень технологична и в интегральном исполнении позволяет достичь плотности упаковки в 50 раз выше, чем при ТТЛ технологии.

При напряжении питания 1,5 В значение высокого потенциала порядка 0,7 В, а низкого – 0,05 В. Так как транзистор Т1 представляет высокоомную нагрузку, потребляемая элементом мощность может быть снижена до чрезвычайно низкой величины (раз в 100 меньше, чем у ТТЛ-элементов). Поэтому элементы И 2 Л нашли широкое применение в БИС (серии КР582, 584).

В сериях ИС невысокой степени интеграции логика И 2 Л не эффективна из-за низкого логического перепада, равного 0,65 В, и поэтому, низкой помехоустойчивости. Кроме того, по быстродействию, вследствие глубокого насыщения транзисторов инвертора, И 2 Л-элементы уступают ТТЛШ-элементам.

Логические элементы на МДП-транзисторах

В настоящее время в логических схемах используются МДП-транзисторы с диэлектриком SiO 2 (МОП-транзисторы).

Анализ МОП-транзисторных логических элементов достаточно прост, т.к. из-за отсутствия входных токов их можно рассматривать отдельно от других элементов даже при работе в цепочке.

На рис. 20 показаны два варианта построения логических элементов на МОП-транзисторах с n-каналами.

а б

Транзисторы Т3 выполняют роль нагрузки.

Логические уровни в обеих схемах не зависят от нагрузки и соответствуют выходным напряжениям открытого и закрытого ключа:

Соответственно, логический перепад составляет:

Напряжение питания E c МОП-логики выбирают в 3…4 раза больше порогового напряжения U o открывания транзисторов. Если U o = 1,5 … 3В, то получаемый логический перепад в 5 … 10В намного превышает значения, свойственные схемам И 2 Л, ЭСЛ и даже ТТЛ (при напряжении питания 4 … 5В). Поэтому МОП-логика обладает повышенной помехоустойчивостью.

Более высоким быстродействием и низким энергопотреблением характеризуется логика на комплементарных транзисторах вследствие причин, рассмотренных ранее. По принципу действия и схемотехнике КМОП-логика очень близка МОП-логике.

Эмиттерно-связанная логика (ЭСЛ)

Вследствие ненасыщенного режима работы транзисторов логический перепад в схеме не превышает 0,65В.

Параметры интегральных логических элементов

Независимо от принадлежности к той или иной серии, все логические элементы характеризуются определенным одним и тем же набором параметров, которые являются справочными данными. Значения же этих параметров обусловлены схемотехническим конструктивным и технологическим исполнением элементов.

Значения параметров, как правило, задаются с запасом и не исчерпывают физических возможностей микросхемы, однако превышать их не следует.

Оценивают микросхемы по следующим основным параметрам:

быстродействию, напряжению питания, потребляемой мощности, коэффициенту разветвления по выходу, коэффициенту объединения по входу, помехоустойчивости, энергии переключения, надежности, стойкости к климатическим и механическим воздействиям. Рассмотрим основные из них.

Уровни выходных напряжений

Техническими условиями для каждой серии логических элементов задаются наибольший и наименьший уровни выходных напряжений, соответствующих логическим единице и нулю при допустимых изменениях напряжения питания, нагрузки, температуры. Напряжение

U 1 вых min соответствует минимальному уровню логической единицы на выходе (для ТТЛ U 1 вых min = 2,4В), а напряжение U 0 вых max – максимальному уровню логического нуля (для ТТЛ U 0 вых max = 0,4В).

Статическая помехоустойчивость

Этот параметр определяет допустимое напряжение помех на входах микросхемы и оценивается для низкого и высокого уровней напряжения.

Статической помехоустойчивостью по низкому уровню считают разность

где U 0 вых max – максимальное допустимое напряжение низкого уровня на выходе нагруженной микросхемы;

U 0 вх max – максимальное допустимое напряжение низкого уровня на входе нагружающей микросхемы.

Помехоустойчивость по высокому уровню определяют так:

здесь U 1 вых min – минимальное напряжение высокого уровня на выходе нагруженной микросхемы; U 1 вх min – минимальное допустимое напряжение высокого уровня на нагружающем входе.

ТТЛ, например, логика еще будет нормально работать, если на ее входе напряжение логического нуля достигнет 0,8В, а напряжение логической единицы снизится до 2В. Таким образом, гарантированный запас помехоустойчивости в обоих состояниях составляет 0,4В. Реальный же запас помехоустойчивости гораздо больше и превышает 1В.

Коэффициент разветвления по выходу

Этот параметр К р аз (нагрузочная способность) определяет максимальное число входов элементов данной серии, которым можно нагружать выходы микросхемы без нарушения ее нормального функционирования.

Коэффициент объединения по входу

К об определяет число логических входов, которые имеет логический элемент.

Простейшие логические элементы выпускаются с 2, 3, 4 и 8 входами. Более сложные устройства содержат и другие входы: адресные, установочные, разрешающие, входы синхронизации и др.

Входные токи

Эти параметры определяют нагрузку, которую представляет рассматриваемая схема, на предшествующую схему или другой источник сигнала. Различают входные токи I 0 вх и I 1 вх при подаче логических нуля или единицы.

Средняя статическая потребляемая мощность

Определяется следующим образом:

где P 0 пот и P 1 пот – мощности, потребляемые интегральным логическим элементом в состоянии логического нуля и логической единицы. Это вытекает из того, что в сложных многоэлементных устройствах в среднем половина логических элементов находится в состоянии 1, а половина – в состоянии 0.

Быстродействие

Характеризуется максимальной частотой смены входных сигналов, при которой еще не нарушается нормальное функционирование устройства.

Инерционность полупроводниковых приборов и паразитные емкости служат причиной того, что каждое переключение сопровождается переходными процессами, отчего фронты импульсов растягиваются.

Для оценки временных свойств микросхем обычно пользуются задержкой распространения сигнала, которая представляет собой интервал времени между входным и выходным импульсами, измеренными на уровне 0,5. Задержки распространения сигнала при включении t 1,0 зд.р. и при выключении t 0,1 зд.р. не равны, поэтому пользуются усредненным параметром t зд.р. ср. = 0,5(t 1,0 зд.р. + t 0,1 зд.р. ).

Для последовательностных устройств (триггеры, счетчики и др.) вводятся некоторые дополнительные временные параметры, обусловленные принципом действия: разрешающее время, длительность входного импульса и др.

В общем случае анализ физических, технологических и схемотехнических особенностей интегральных логических элементов показывает, что можно создать различные их варианты, но их особенностью будут либо относительно высокое (высокое) быстродействие при низкой экономичности, либо высокая экономичность при относительно низком (низком) быстродействии. Обобщенные характеристики известных типов интегральных логических элементов приведены в таблице 3.

Цифровые логические микросхемы, выполненные на комплементарных МОП транзисторах (КМОП микросхемы)

Логические КМОП (КМДП) инверторы

Микросхемы на комплементарных МОП транзисторах (КМОП-микросхемы) строятся на основе МОП транзисторов с n- и p-каналами. Эти транзисторы часто называют МДП транзисторами, поэтому микросхемы тоже могут называться КМДП (иностранное название: CMOS logic). Один и тот же входной потенциал открывает транзистор с n-каналом и закрывает транзистор с p-каналом. При формировании логической единицы открыт верхний транзистор, а нижний закрыт. В результате ток через КМОП схему не протекает.

При формировании логического нуля открыт нижний транзистор, а верхний закрыт. И в этом случае ток от источника питания через микросхему не протекает. Простейший логический элемент — это инвертор. Принципиальная схема инвертора, выполненного на комплементарных МОП транзисторах, приведена на рисунке 1.

Рисунок 1. Принципиальная схема инвертора, выполненного на комплементарных МОП транзисторах (КМОП-инвертор)

Схему, изображенную на рисунке 1 часто называют базовым элементом КМОП-микросхем. На этой схеме для упрощения понимания принципов работы КМОП микросхемы не показаны защитные и паразитные диоды. Особенностью микросхем на комплементарных МОП транзисторах (КМОП-микросхем) является то, что в этих микросхемах в статическом режиме ток практически не потребляется. Потребление тока происходит только в момент ее переключения из единичного состояния в нулевое и наоборот. Этот ток вызван двумя причинами — одновременным переходом верхнего и нижнего МОП транзисторов в активный режим работы и перезарядом паразитной ёмкости нагрузки.

В результате этой особенности КМОП-микросхем, они обладают преимуществом перед рассмотренными ранее видами цифровых микросхем — потребляют ток в зависимости от поданной на вход тактовой частоты. Примерный график зависимости потребления тока КМОП-микросхемы в зависимости от частоты ее переключения приведен на рисунке 2

Рисунок 2. Зависимость тока потребления КМОП микросхемы от частоты

Подробно зависимость тока потребления КМДП микросхем от частоты переключения логических вентилей приведено в документе «CMOS Power Consumption and Cpd Calculation» фирмы Texas Instruments [7].

Логические КМОП (КМДП) элементы «И»

В этой схеме можно было бы применить в верхнем плече обыкновенный резистор, однако при формировании низкого уровня сигнала схема постоянно потребляла бы ток. Вместо этого, в качестве нагрузки используются p-МОП транзисторы. Эти транзисторы образуют активную нагрузку. Если на выходе требуется сформировать высокий потенциал, то транзисторы открываются, а если низкий — то закрываются.

Обратите внимание, что КМОП топология логического элемента «2И-НЕ» получается еще проще. В качестве нижних двух полевых транзисторов используется единый n канал, на котором формируется два затвора (двухзатворный полевой транзистор). Упрощенная топология логического элемента на комплементарных МОП транзисторах приведена в [6] и показана на рисунке 4.

Рисунок 4. Упрощенная топология логического элемента

Такая топология позволяет занимать на кристалле интегральной микросхемы минимальное место и получать максимальную плотность логических элементов. Способом, подобным приведенному на рисунке 4 легко могут быть получены логические элементы «3И-НЕ», «4И-НЕ», «8И-НЕ» и т.д.

В приведённой на рисунке 3 схеме логического КМОП-элемента «2И-НЕ», ток от источника питания на выход КМОП-микросхемы будет поступать через один из транзисторов, если хотя бы на одном из входов (или на обоих сразу) будет присутствовать низкий потенциал (уровень логического нуля). Если же на обоих входах логического КМОП-элемента «И» будет присутствовать уровень логической единицы, то оба p-МОП транзистора будут закрыты и на выходе КМОП микросхемы сформируется низкий потенциал. В этой схеме, так же как и в схеме, приведенной на рисунке 1, если транзисторы верхнего плеча будут открыты, то транзисторы нижнего плеча будут закрыты, поэтому в статическом состоянии ток КМОП-микросхемой от источника питания потребляться не будет.

Рисунок 5. Условно-графическое изображение логического элемента «2И-НЕ»

Таблица 1. Таблица истинности КМОП-микросхемы, выполняющей логическую функцию «2И-НЕ»

| x1 | x2 | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Логические КМОП (КМДП) элементы

Рисунок 6. Принципиальная схема логического элемента «ИЛИ-НЕ», выполненного на комплементарных МОП транзисторах

В схеме КМОП логического элемента в качестве нагрузки используются последовательно включенные p-МОП транзисторы. В ней ток от источника питания на выход КМОП микросхемы будет поступать только если все транзисторы в верхнем плече будут открыты, т.е. если сразу на всех входах будет присутствовать низкий потенциал (уровень логического нуля). Если же хотя бы на одном из входов будет присутствовать уровень логической единицы, то верхнее плечо двухтактного каскада, собранного на КМОП транзисторах, будет закрыто и ток от источника питания поступать на выход КМОП-микросхемы не будет.

Рисунок 7. Условно-графическое изображение элемента «2ИЛИ-НЕ»

Таблица 2. Таблица истинности МОП микросхемы, выполняющей логическую функцию «2ИЛИ-НЕ»

| x1 | x2 | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

В настоящее время именно КМОП-микросхемы получили наибольшее развитие. Причём наблюдается постоянная тенденция к снижению напряжения питания данных микросхем. Первые серии КМОП-микросхем, такие как К1561 (иностранный аналог C4000В) обладали достаточно широким диапазоном изменения напряжения питания (3..18В). При этом при понижении напряжения питания у конкретной микросхемы понижается её предельная частота работы. В дальнейшем, по мере совершенствования технологии производства, появились улучшенные КМОП-микросхемы с лучшими частотными свойствами и меньшим напряжением питания, например, SN74HC.

Особенности применения КМОП-микросхем

Первой и основной особенностью КМОП-микросхем является большое входное сопротивление этих микросхем. В результате на ее вход может наводиться любое напряжение, в том числе и равное половине напряжения питания, и храниться на нём достаточно долго. При подаче на вход КМОП-элемента половины питания открываются транзисторы как в верхнем, так и в нижнем плече выходного каскада, в результате микросхема начинает потреблять недопустимо большой ток и может выйти из строя [3]. Вывод: входы цифровых КМОП-микросхем ни в коем случае нельзя оставлять неподключенными!

Второй особенностью КМОП-микросхем является то, что они могут работать при отключенном питании. Однако работают они чаще всего неправильно. Эта особенность связана с конструкцией входного каскада. Полная принципиальная схема КМОП-инвертора приведена на рисунке 8.

Рисунок 8. Полная принципиальная схема КМОП-инвертора

Диоды VD1 и VD2 были введены для защиты входного каскада от пробоя статическим электричеством. В то же самое время при подаче на вход КМОП-микросхемы высокого потенциала он через диод VD1 попадёт на шину питания микросхемы, и так как онапотребляет достаточно малый ток, то КМОП микросхема начнёт работать. Однако в ряде случаев этого тока может не хватить дляпитания микросхем. В результате КМОП микросхема может работать неправильно. Вывод: при неправильной работе КМОП микросхемы тщательно проверьте питание микросхемы, особенно выводы корпуса. При плохо пропаянном выводе отрицательного питания его потенциал будет отличаться от потенциала общего провода схемы.

Третья особенность КМОП микросхем связана с паразитными диодами VD3 и VD4, которые могут быть пробиты при неправильно подключенном источнике питания (микросхемы ТТЛ выдерживают кратковременную переполюсовку питания). Для защиты КМОП микросхем от переполюсовки питания следует в цепи питания предусмотреть защитный диод.

Четвёртая особенность КМОП-микросхем — это протекание импульсного тока по цепи питания при ее переключении изнулевого состояния в единичное и наоборот. В результате при переходе с ТТЛ микросхем на КМОП микрохемы-аналоги резко увеличивается уровень помех. В ряде случаев это важно, и приходится отказываться от применения КМОП микросхем в пользу ТТЛ или BICMOS микросхем.

Логические уровни КМОП-микросхем

Логические уровни КМОП-микросхем существенно отличаются от логических уровней ТТЛ микросхем. При отсутствии тока нагрузки напряжение на выходе КМОП-микросхемы совпадает с напряжением питания (логический уровень единицы) или с потенциалом общего провода (логический уровень нуля). При увеличении тока нагрузки напряжение логической единицы может уменьшается на 2,8В от напряжения питания (Uп=15В). Допустимый уровень напряжения на выходе цифровой КМОП микросхемы (серия микросхем К561) при пятивольтовом питании показан на рисунке 9.

Рисунок 9. Уровни логических сигналов на выходе цифровых КМОП-микросхем

Как уже говорилось ранее, напряжение на входе цифровой микросхемы по сравнению с выходом обычно допускается в больших пределах. Для КМОП-микросхем договорились о 30% запасе. Границы уровней логического нуля и единицы для КМОП-микросхем при пятивольтовом питании приведены на рисунке 10.

Рисунок 10. Уровни логических сигналов на входе цифровых КМОП-микросхем

При уменьшении напряжения питания границы логического нуля и логической единицы можно определить точно так же (разделить напряжение питания на 3).

Семейства КМОП-микросхем

Дата последнего обновления файла 15.04.2020

Понравился материал? Поделись с друзьями!

Вместе со статьей «КМОП микросхемы» читают: